数字IC设计APR6

- 生活百科

- 2026-03-19

- 415

学习目标:

die size越小。wafer上面生产出来的芯片越多,关系到cost

die size 要考虑的内容

die size 包括哪些方面:

die size 和chip cost的关系

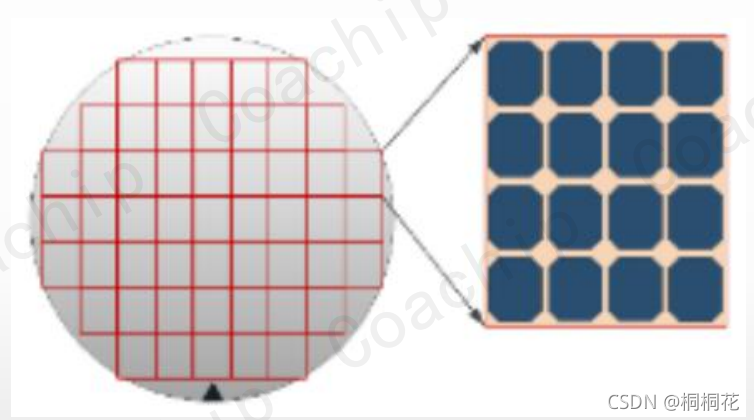

左边是wafer,右边小方块是的full chip。

die size: lower chip cost

die size: chip cost

chip size越小,wafer上die越多,wafer价格固定,可以降低cost。

MFU:芯片die的利用率。

假设厂规定80%以上不会对wafer产生额外的生产成本,低于80%时,例如MFU为75%,会额外增加200$。但是有时,MFU低会导致芯片die数目增加,此时芯片生产得到的价格大于200$。

有些大公司为了得到更好的chip故意低于厂的MFU(但是这一般涉及很多部门的讨论与决策,一般公司都是meet MFU的)。

Typ

lO

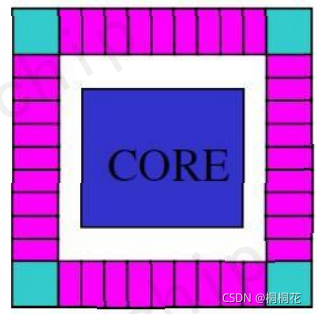

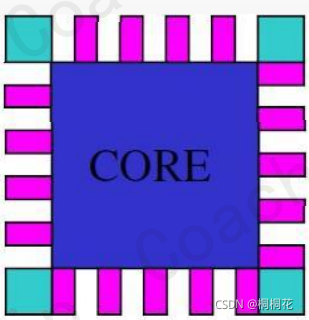

core只需要一定大小,但是和外界交互信号特别多,已经超过core的size。

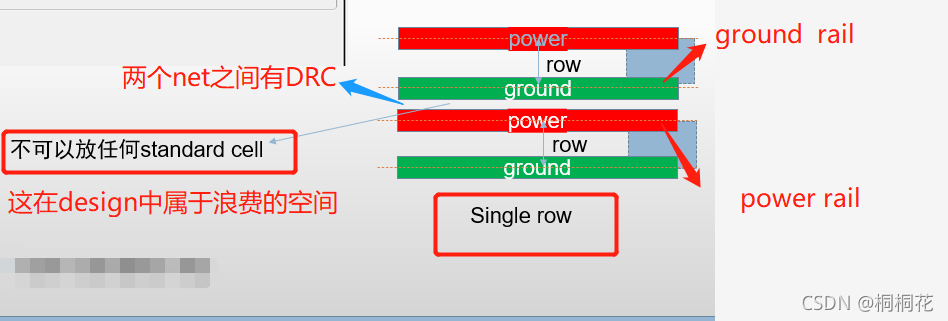

从下图可以看到,白色区域无法放置其他东西,这部分space被浪费了。

这种情况一般不希望看到。

core

core size比较大,IO比较少。 但是core size很难减小,IO高度是一定的,外面多余大的部分,可以插入ESD之类的。

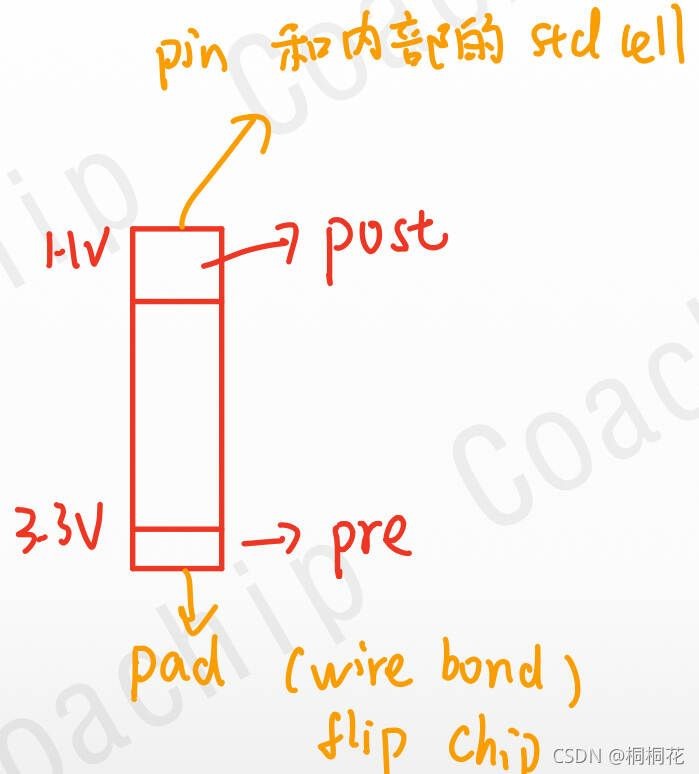

IO的两种power

低压post ,高压pre 。

cell 的摆放或core area内row 的位置

std cell摆放在哪里 :设置rows的位置,构成 core area内可以放置 cells 的地方。

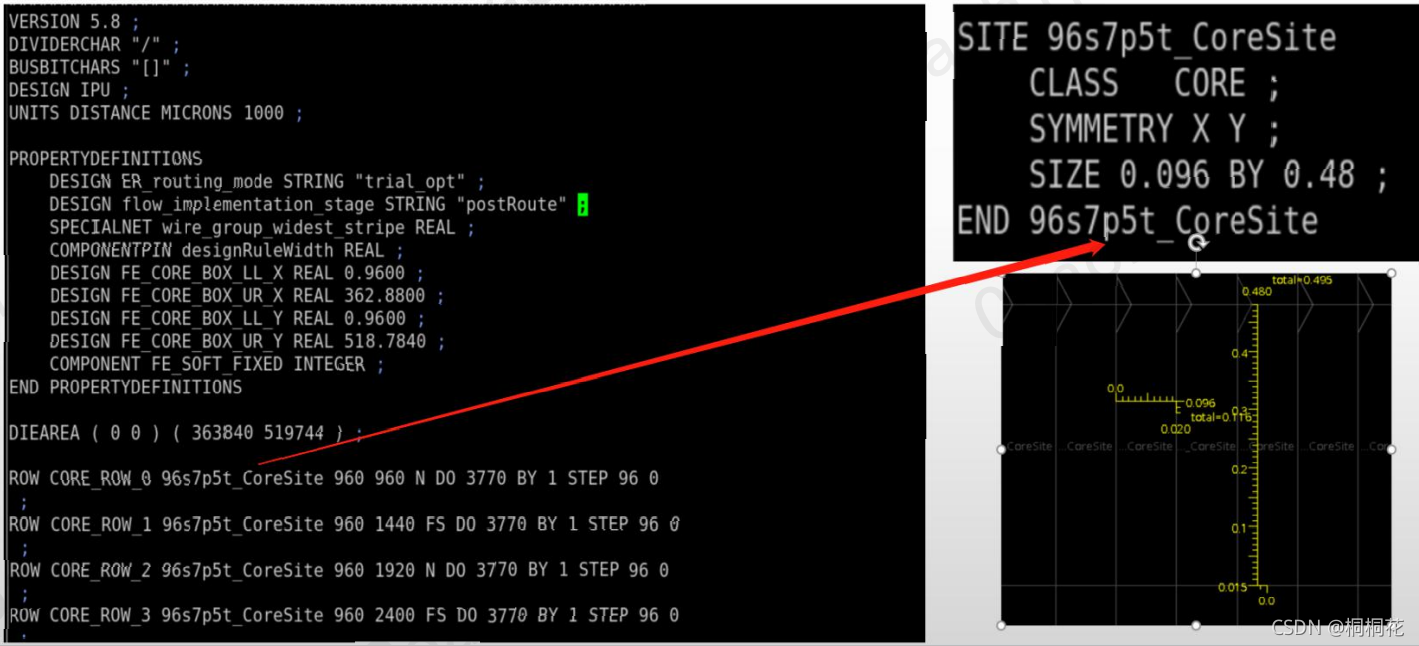

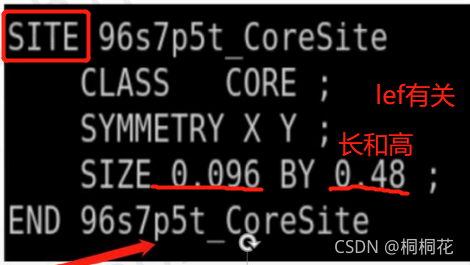

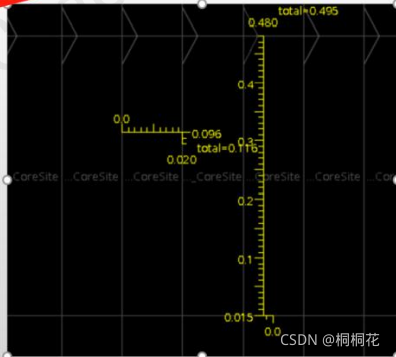

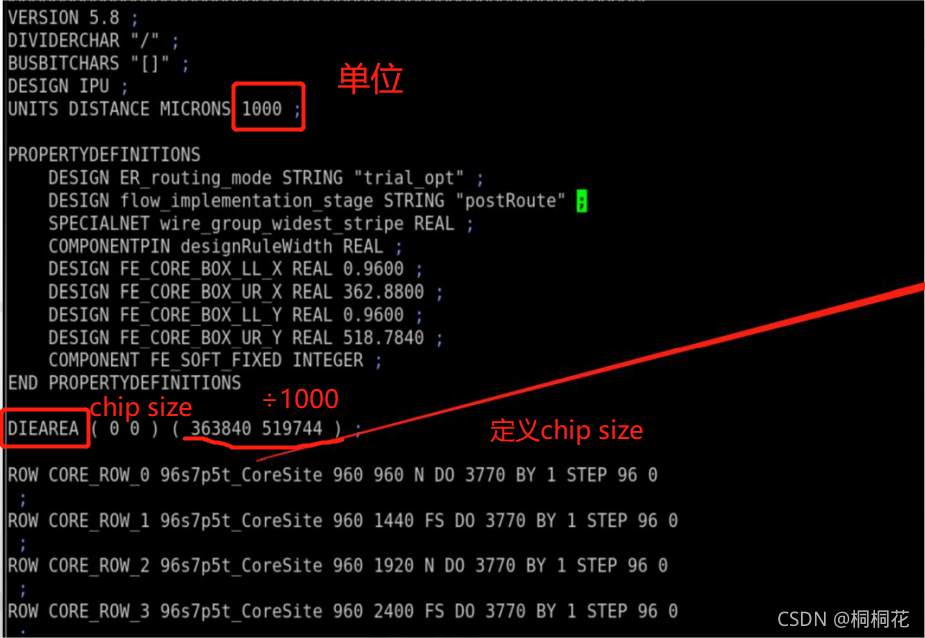

定义site(row的位置),std cell 0.096的长度和0.48的宽度,或者是整数倍

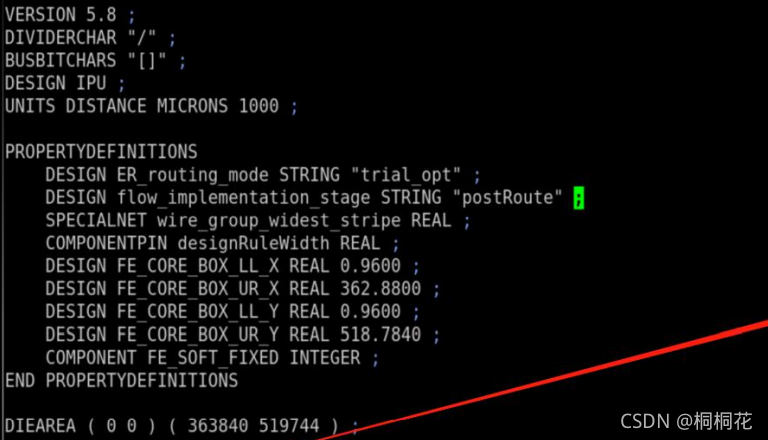

1000:单位是0.001um(是将1um分成1000个unit)。

lef文件里面定义chip size的,用那个坐标除了1000,相当于坐标×0.001。

size/shape/area/

高设计利用率(high ):

die size越小,带来的挑战越大

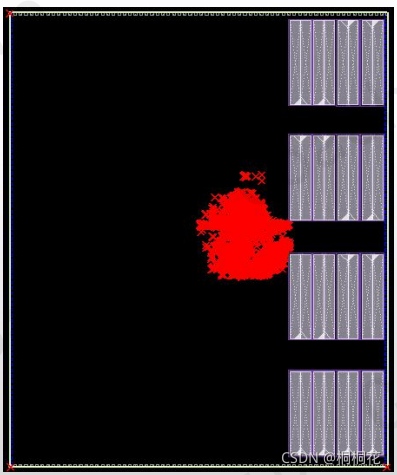

红色的区域放大,在APR工具里面都是X。

假如这块区域只允许绕15跟线,实际为了布通道,用了30 根线,超过了允许布线的数目,打X。

X的数目非常多,线绕不通,功能会失败

解决方法:

1、将放置不合理的移到另一个地方,减轻

2、 ,人为加一些约束,将放大。

3、...

总之,将这块地方推开,让它占用更大的资源。

Die 和core之间的间距

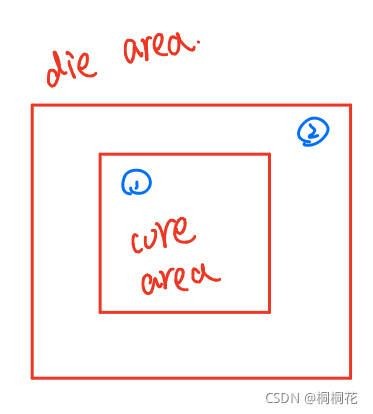

chip和block level都有die area和core area。

chip/top level:

①std cell

②GPIO(IO一般在top中,block里面是没有IO的,有时候block布局规划必须有IO,top切给block IO,这种情况,一般是经验丰富懂top的人去处理这部分IO)

block level

①std cell

②port (一般情况没有IO)

在top上,两个block之间通过port相互连接,port实际上是物理的线,不占用base layer。

base layer:简单理解为金属层以下的层级 (Metal 1以下的那些层次,我们pr时看不到,只能再gds里面看到):例如掺杂,n/p阱,poly等这些;

metal layer:同理 (Metal 1及以上的层次,pr时可见)

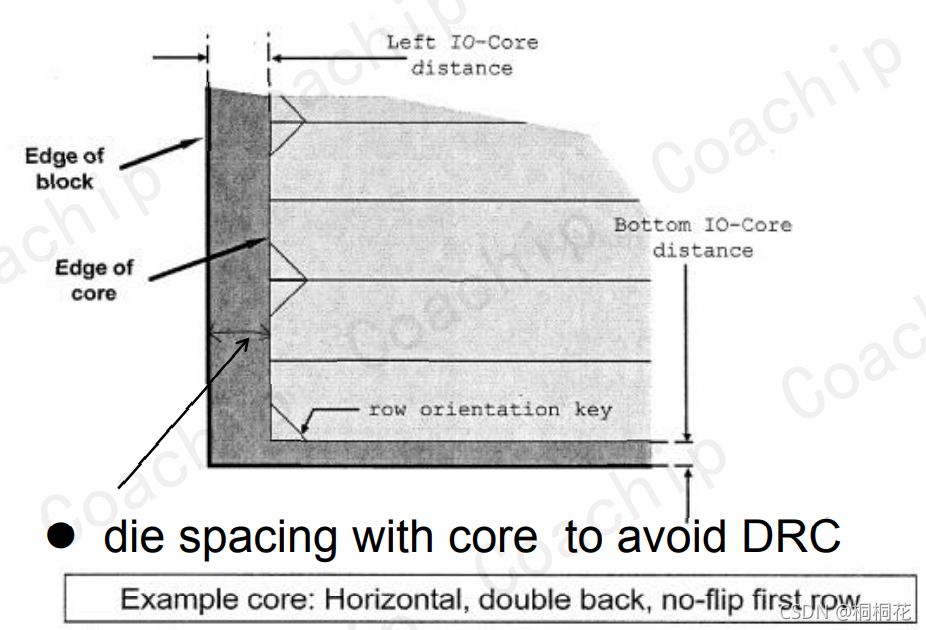

die area和core area之间留一些,阻止DRC;另一种情况,

如,两个block拼在一起,之间没有。两个block上各有一条线靠近边界。

两个block单独做spef抽取,STA,中间cover部分没有做,合到top上,如果中间部分时序比较紧张,会导致时序违例。

为了安全起见,die area和core area之间留1-2微米的,这个里面不放任何std cell,不 track。

back

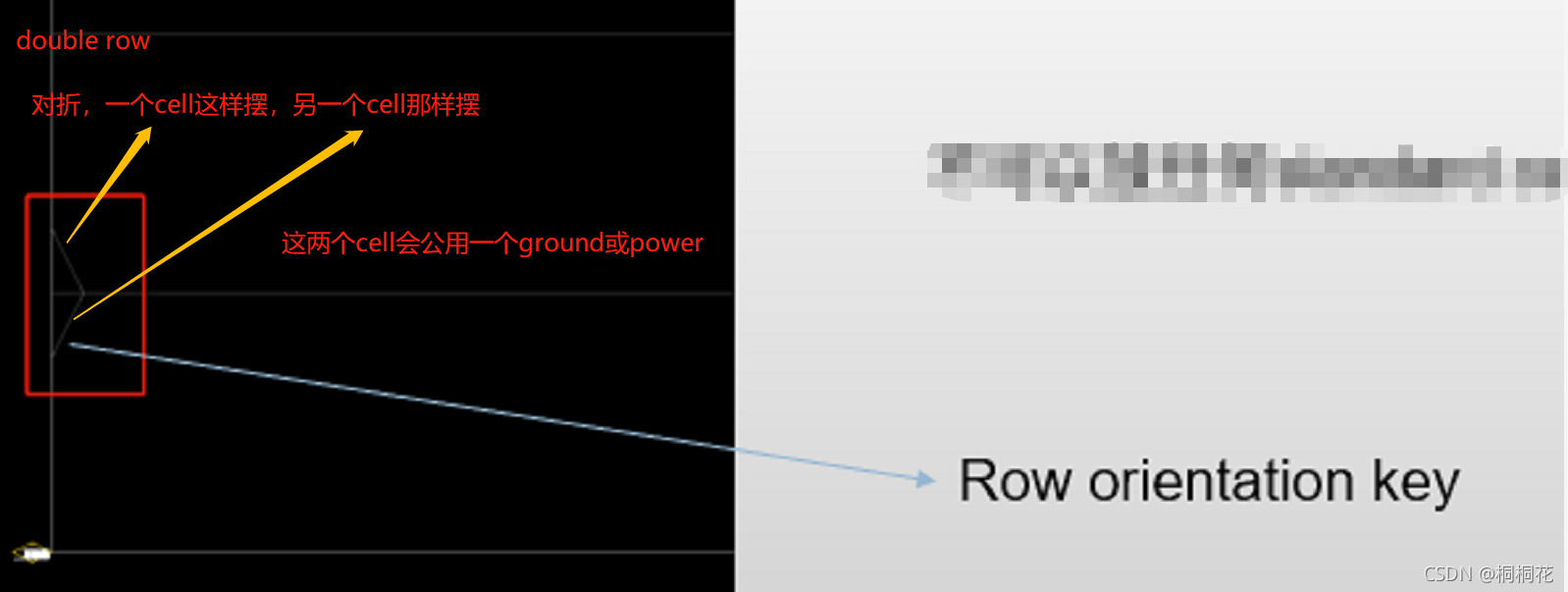

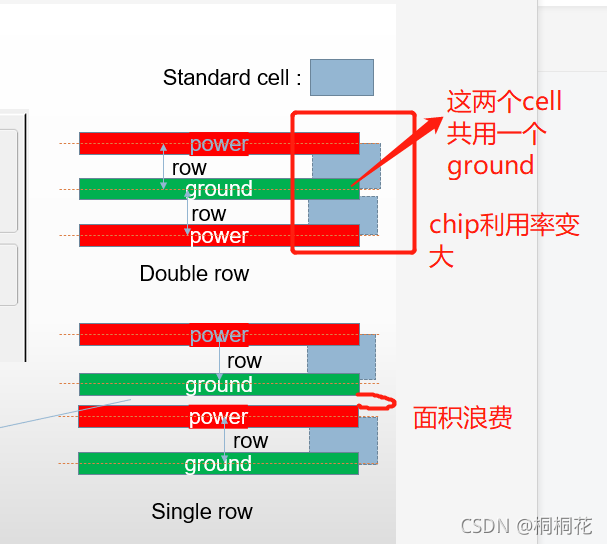

row的一个对折

row

集成电路刚开始发展时用到的,EDA还不智能。

row

现在基本用到这种方法

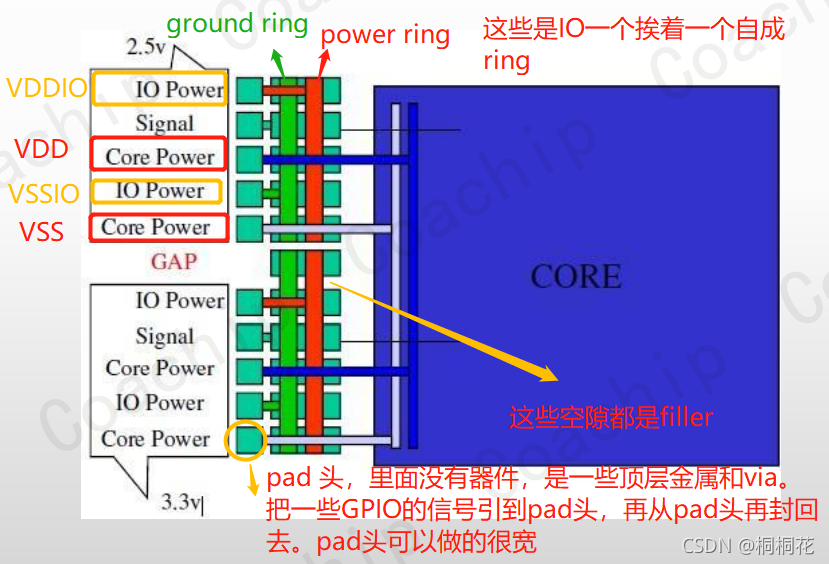

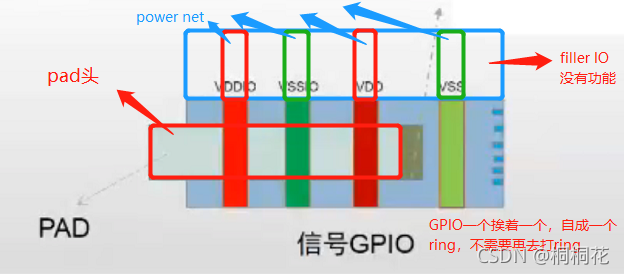

IO PAD /size/

正确的I/O pad放置和选择对芯片的正确功能非常重要。

有三种类型的I/O pad:power,和。(还有一些没有功能的,只是用来保证DRC或其他ESD东西而存在的。)

一般情况下IO高度是一样的,对应的线的名字也是一样的。

供电最好以网状的形状,布满全局,保证供电的强壮。

放大其中一个IO

正常IO有四个电源线

信号IO是一个挨着一个放的,自成ring

Macro/IP Size and

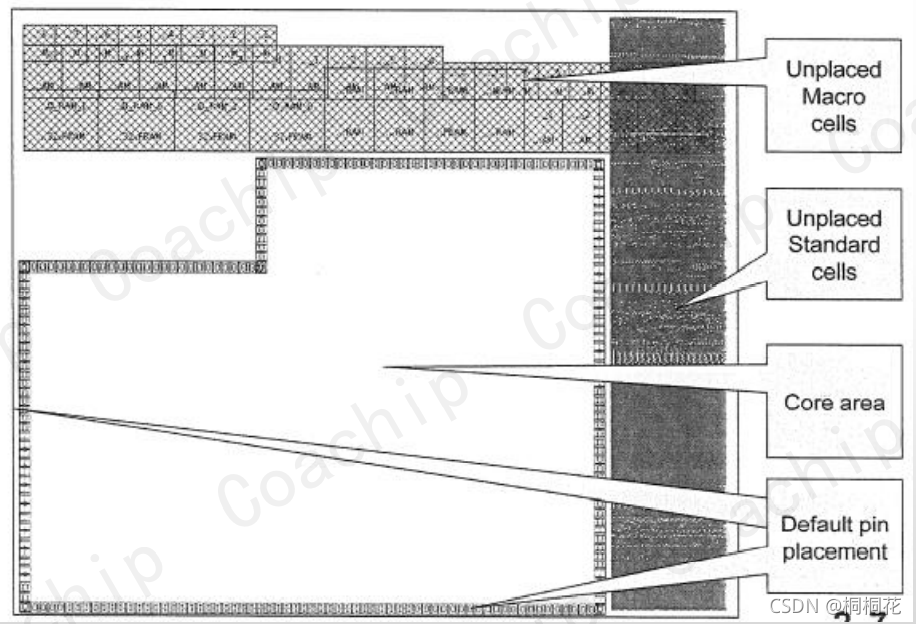

实际读入,根据一些, 会默认创建创建一个die size。

Die Size

die area:

IO pad area

core area

chip area = core area+ power ring area + PAD ring area(指IO pad的区域)

core area = RAM area + IP area + STD cell area

=Marco area + STD cell area

(RAM area + IP area统称Marco)RAM area = RAM ownphysical area + RAM powerring area + keepout area+mbist areaRAM PG ring area的计算

Area = x * d+y*d+ x*d + y *d + d*d*4 =周长*d+d* d*4

(d是ring的宽度 )(这种case现在已经很少了)

IP area = total physical areaof IP x (1+ 3%~5%)

STD cell area=standard cell physical area / utilization(面积利用率)

keepout + mbist area =RAM own physical area x10%Die Shape

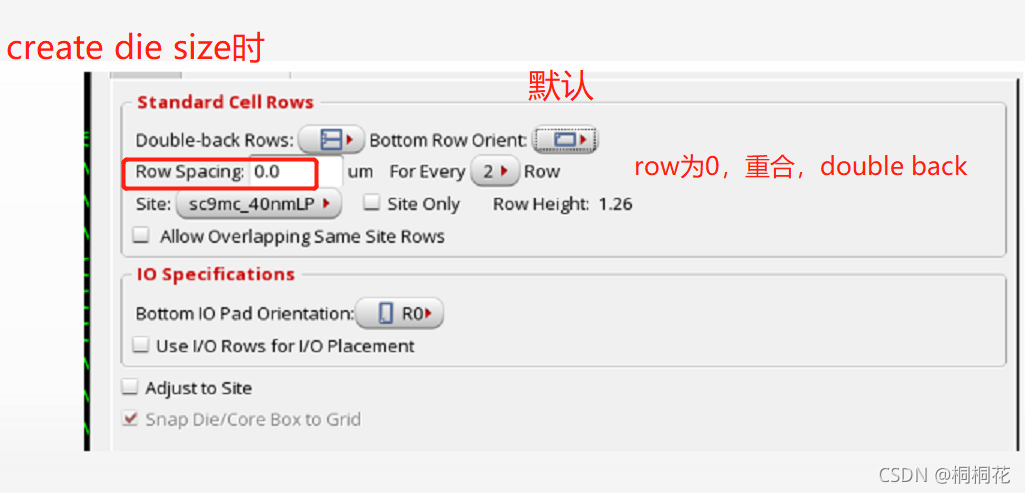

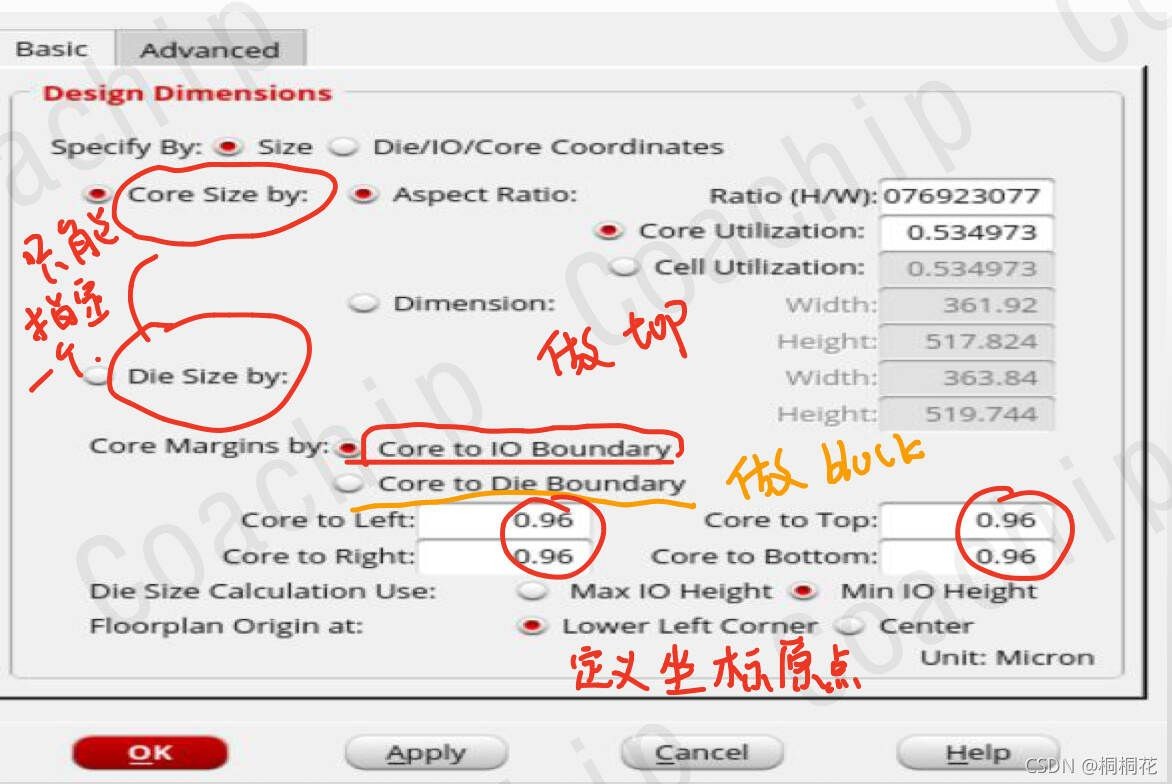

如何创建chip size:

(1)通过命令行

floorPlan -site 96s7p5t_Coresite -flip s -su {1.428 0.6 0.96 0.96 0.96 0.96}

//site,指定特定工艺的site

//16nm之前,包括22、28、40、90,cmos工艺,后来16nm以下是FINFET工艺,对格点要求很高

//指定core site的名字96s7p5t_Coresite

//1.428,chip的长宽比

//0.6指的是std cell利用率是0.6,std cell要做到1/0.6

// 后面四个数字{0.96 0.96 0.96 0.96}是die size和core size之间留的距离。(2)通过gui

(3)更改def

不规则的形状,通过上两种方法无法创建的。

做top的人,的时候,在规划模块的时候,认为这种形状更有利于顶层走线或为了其他模块让步一些东西。

上一篇:野生植物单株序列(2)--蒲公英

下一篇:赤翅蜂的作用与功效

发表评论